3纳米芯片,可能连苹果都玩不起

编辑 | 陈伊凡

卡在2022年的最后几天,台积电兑现了年内量产3nm工艺芯片的承诺。

12月24日,据中国台湾媒体《经济日报》报道,台积电将于下周在南科园区的3nm工厂举办量产暨扩厂典礼。

按照台积电的规划,这座总投资高达6000亿新台币(约合人民币1360亿)的超级工厂,在满产后的月产能将实现6万片12英寸晶圆。这也创下了台积电单笔投资建厂的纪录,作为对比,台积电2020年在美国投建的5nm工厂投资额为120亿美元(约合人民币838亿)。

只不过,现阶段似乎没有下游厂商,能为这项奢侈的技术买单了。

01

买不起的芯片,撑不住的市场

在台积电宣布3纳米制程量产之前,台积电在先进制程上的唯一对手三星宣布成功量产3nm芯片。但虎嗅向多位业内人士了解,三星的先进制程芯片,一直卡在良率上不去。因为有代工市场的压力,三星往往会早一些宣布自己的制程进展。

而在头部代工厂的研发专家表示,三星3纳米芯片的首位客户是一家国内的挖矿芯片厂商,原因是挖矿芯片的制程要求单一,并不是完整的工艺平台,光罩数量也少很多。通常情况下,芯片上的晶体管会按照一定比例分配给逻辑(负责运算)和SRAM(负责存储),上述专家表示,对于挖矿芯片来说,基本只用到了前者,这对于代工厂来说更容易实现。

所谓SRAM,即静态随机存储器,这种存储器只要保持通电,里面储存的数据就可以恒常保持。

并且,挖矿芯片厂商希望能够尽可能使用高性能,三星在试验阶段的用户会给出很好的优惠。

因此,相比之下,业界认为对于向来求稳的台积电来说,一旦他们公布量产,良率上能够相对可靠。但即便如此,似乎没有多少客户愿意买单,或者买得起这个单。

11月,台媒《电子时报》援引产业链知情人士的消息指出,台积电的某位头部客户已经大幅削减了3nm芯片的订单。

虎嗅根据公开信息查询,目前包括苹果、英伟达、英特尔、AMD、高通、联发科都表达了让台积电代工3nm芯片的意愿,但在上述公司中,没有一家明确公布了3nm产品的时间表。

这与今年年初各家提前预约3nm芯片产能的光景形成了强烈的对比。从抢占产能到大客户砍单,为什么各大厂商突然对3nm芯片失去了兴趣?

一个最直接的原因是,这项新技术真的太贵了。

此前,英伟达在发布4nm制程的RTX 40系列显卡时,CEO黄仁勋就曾吐槽过,“现在的芯片代工不是贵一点点,而是巨幅涨价。”

而进入3nm制程后,代工端给出的价格要更加夸张。根据Digitimes的数据,未来3nm芯片量产后,晶圆的单片价格将突破20000美元,相比于7nm芯片翻了一番。

芯片设计厂商对于代工价格上涨不满,而台积电也是有苦难言。

从成本核算的角度来看,第三方分析机构IBS曾算过一笔账,晶圆厂在3nm制程的工艺研发投入达到40亿美元-50亿美元,建一座3纳米制程、每月生产4万片的生产线,成本约为150亿美元-200亿美元,这还只是晶圆厂的投入。

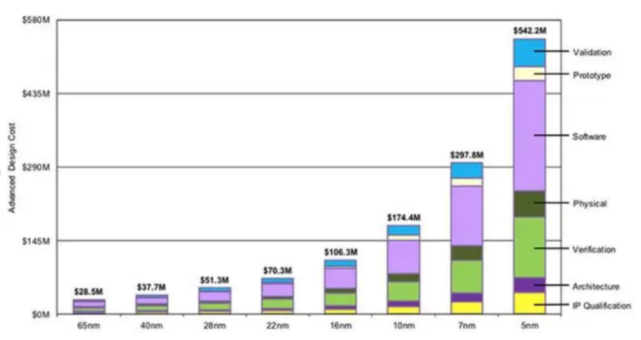

先进制程芯片的开发费用同样不遑多让,其研发费用主要包括芯片设计、IP、EDA、设备等,根据第三方半导体研究机构Semi engineering计算,28纳米制程的开发费用大约为5130万美元,到16纳米制程需要投入1亿美元,到5纳米制程节点,这个费用达到5.42亿美元。

02

相比于此前的工艺节点,台积电此次发布的三纳米制程的工艺技术略显无力。毫无疑问,在先进制程上的竞争,半导体厂商依然会一直卷下去。但现在谁能为其买单?可能连台积电自己也说不准。

科技人物

关注公众号:拾黑(shiheibook)了解更多

[广告]赞助链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

让资讯触达的更精准有趣:https://www.0xu.cn/

腾讯科技

腾讯科技

关注网络尖刀微信公众号

关注网络尖刀微信公众号