ASML 1nm光刻机完成:摩尔定律尚未结束

新智元报道

新智元报道

来源:Sparrows NEWS

编辑:小匀

【新智元导读】根据日媒的报道,在不久前举办的线上活动中,欧洲微电子研究中心IMEC首席执行官兼总裁Luc Van den hove在线上演讲中表示,在与ASML公司的合作下,更加先进的光刻机已经取得了进展。

摩尔定律的终点是什么?随着5nm光刻技术的大规模生产和3nm的突破,摩尔定律的终结变得越来越难以捉摸。可以肯定的是,随着过程的进一步改进,其成本将成倍增加。

根据日本媒体Mynavi的报道,欧洲微电子研究中心IMEC首席执行官兼总裁Luc Van den hove在最近一次在线活动的在线演示中表示,与ASML合作已朝着更先进的光刻技术取得了进展。

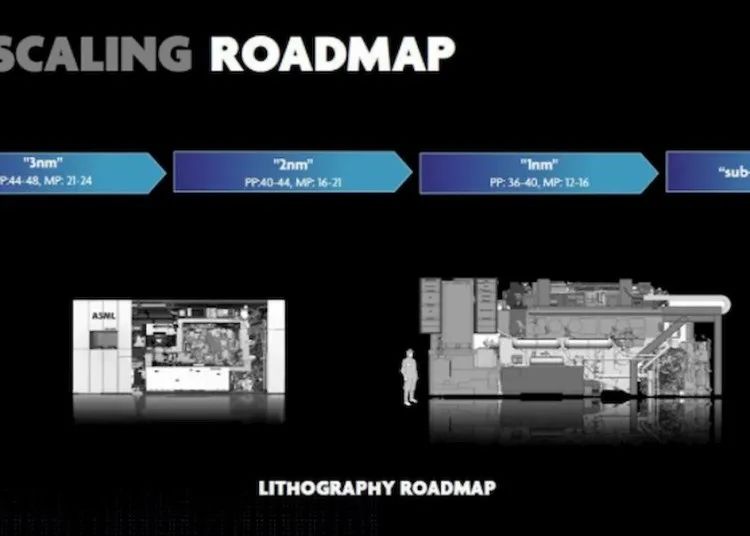

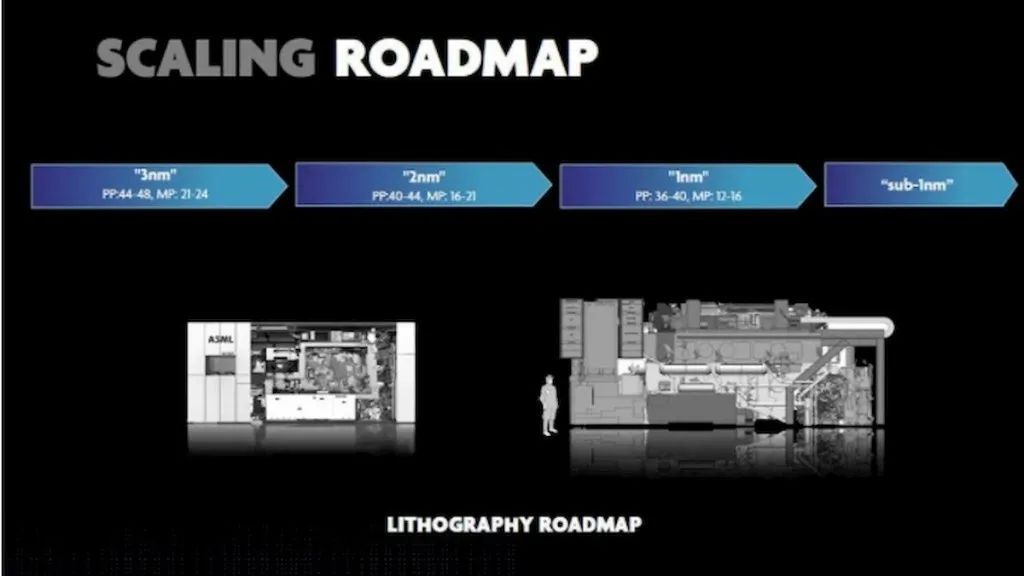

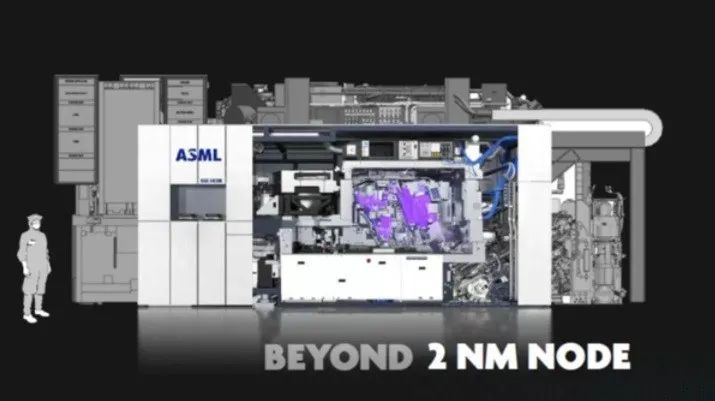

本月中旬,ITF论坛在日本东京举行。在论坛上,与ASML合作开发光刻技术的比利时半导体研究组织IMEC在微尺度级别上宣布了3nm及以下工艺的技术细节。至少就目前而言,ASML为3m ,2nm, 1.5nm,1nm甚至Sub 1nm制定了清晰的路线图,而1nm时代将使光刻机的尺寸大大增加。

EUV光刻系统的技术路线图,用于逻辑器件的工艺小型化

ASML几乎完成了1nm光刻机的设计

IMEC首席执行官兼总裁Luc Van den hove作了第一场主旨演讲,概述了该公司的研究成果,并强调了与ASML的密切合作,下一代高分辨率EUV光刻,高NA EUV光刻的商业化。IMEC Inc.强调了将尺寸缩小至1nm及以下的过程将继续进行。

包括日本在内的许多半导体公司已经退出了工艺的小型化,声称摩尔定律已告终结,或者说摩尔定律过于昂贵且无利可图。尽管日本许多光刻工具制造商已经退出了EUV光刻开发阶段,但半导体研究机构IMEC和ASML一直在合作开发EUV光刻,这对于超精细规模至关重要。

IMEC宣布了1nm及以下工艺的路线图

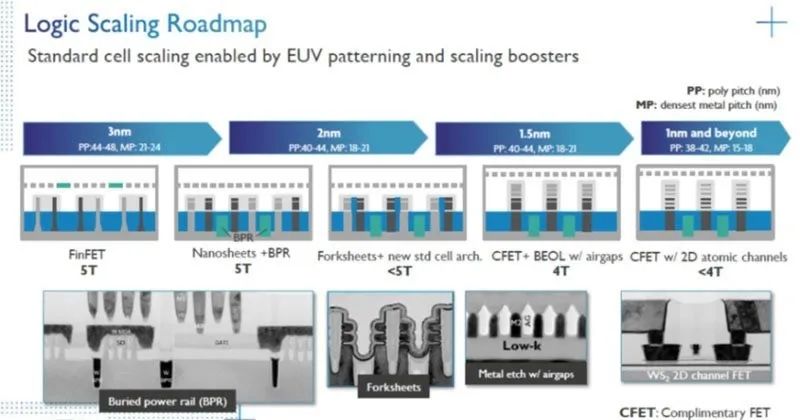

IMEC将在2020年ITF日本大会上提出3nm,2nm,1.5nm和1nm以下逻辑器件小型化的路线图。

IMEC的逻辑设备小型化路线图

PP是多晶硅互连的间距(nm),MP是上游技术节点名称下的精细金属布线的间距(nm)。应该注意的是,过去的技术节点是指最小的工艺尺寸或门的长度,但是现在它们只是“标签”,而不是指位置的物理长度。

EUV的高NA对进一步小型化至关重要

根据台积电和三星电子的说法,从7nm工艺开始,一些工艺引入了NA = 0.33的EUV光刻设备,而5nm工艺也实现了频率的提高,但对于2nm之后的超精细工艺,分辨率更高且更高。需要实现光刻设备NA(NA = 0.55)。

EUV光刻系统的技术路线图,用于逻辑器件的工艺小型化

根据IMEC的说法,ASML已经完成了作为NXE:5000系列的高NA EUV曝光系统的基本设计,但计划于2022年实现商业化。

ASML过去一直与IMEC密切合作,以开发光刻技术,但为了使用高NA EUV光刻工具开发光刻工艺,已在IMEC校园内建立了新的“ IMEC-ASML高NA EUV实验室”,以促进联合研究和使用高NA EUV光刻工艺的工具开发光刻工艺。该公司还计划与材料供应商合作开发掩膜和抗蚀剂。

ASML在过去与IMEC密切合作开发光刻技术,但开发光刻过程使用高NA EUV光刻工具,一个新的「IMEC-ASML高NA EUV实验室」已经建立在IMEC校园促进联合研究和开发的光刻过程使用高NA EUV光刻过程的工具。该公司还计划与材料供应商合作开发口罩和防腐蚀剂。

参考链接:

https://sparrowsnews.com/2020/12/01/asml-1nm-lithography/

关注公众号:拾黑(shiheibook)了解更多

[广告]赞助链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

让资讯触达的更精准有趣:https://www.0xu.cn/

关注网络尖刀微信公众号

关注网络尖刀微信公众号随时掌握互联网精彩

- 1 中法友谊蕴山水 7904058

- 2 你以为的进口尖货 其实早已国产了 7808234

- 3 张荣恭:敢宣布“台独”大陆立刻动手 7712045

- 4 盘点2025大国重器新突破 7616669

- 5 部分银行上调存款利率 7521325

- 6 美国称将调整与中国经济关系 7427711

- 7 大雪吃三宝是指哪三宝 7331049

- 8 尖叫之夜直播 7234233

- 9 男子在三亚海滩捅死3人 警方通报 7139641

- 10 周末去哪玩?雪场“不打烊” 7040715

新智元

新智元