3纳米、2纳米、1纳米芯片该如何造?

来源:EETOP编译

来源:EETOP编译

目前台积电和三星正在加紧开发他们的3nm和2nm技术,目前预计分别在2022年和2024年推出。1nm及以上工艺也正在进行中,但是距离仍然很远。

业界希望从3nm开始,从当今的finFET晶体管过渡到全能栅极或称为环绕式栅极FET(GAA)。在2nm甚至更高的制程下,业界正在研究当前和新版本的GAA晶体管。

在这些节点上,芯片制造商可能会需要新设备,例如下一代极紫外线(EUV)光刻技术。新的沉积,蚀刻和检查/计量技术也在研究中。

不用说,这里的设计和制造成本是天文数字。根据IBS的数据,3nm芯片的设计成本为6.5亿美元,而5nm器件的设计成本为4.363亿美元,而7nm的设计成本为2.223亿美元。而对于2nm、1nm要花费多少,现在评估还为时过早。

并非所有设计都需要高级节点。实际上,成本上升正促使许多人探索其他选择,例如高级封装技术。获得扩展优势的一种方法是将更多小芯片封装在一起。

半导体工程公司已研究了下一代晶体管、晶圆厂工具、材料、封装和光子学方面的领先技术。

新型晶体管和材料

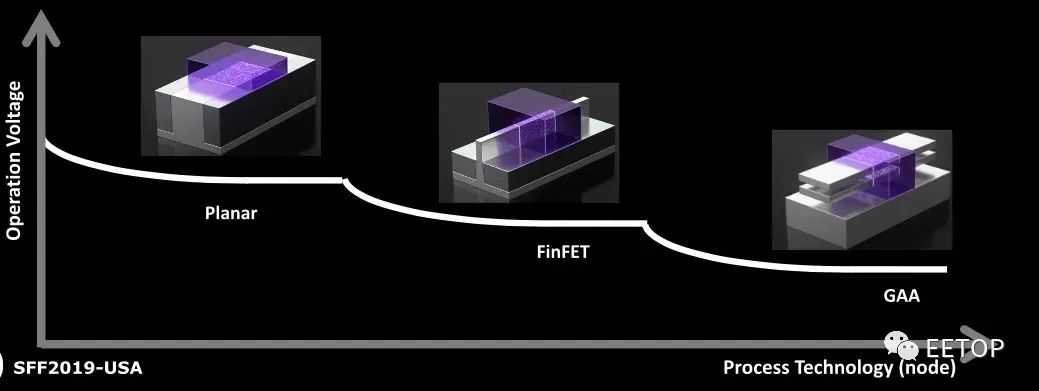

晶体管作为芯片中的关键构件之一,为器件提供了开关功能。几十年来,基于平面晶体管的芯片是市场上最先进的器件。

到了20纳米时,平面晶体管撞到了天花板。为此英特尔在2011年转向22nm的finFET,随后用在了16nm / 14nm。在finFET中,电流的控制是通过在鳍的三个侧面的每一个上实现栅极来实现的。

借助finFET,芯片制造商继续采用传统的芯片缩放技术。但是,当鳍片宽度达到5nm时,finFET可能会失去优势无法进一步微缩,这将发生在3nm节点附近。因此,选择3nm工艺的代工厂希望在2022年迁移到下一代晶体管,称为纳米片FET。纳米片式FET属于栅极全环绕式FET的范畴。

纳米片式FET是鳍片式FET的延伸。它是在其侧面有一个栅极包裹的鳍片FET。纳米片会在3nm处出现,可能会延伸到2nm或更高。

图1:平面晶体管与finFET与纳米片FET。突破来源:三星

还有一些其他的选择也属于GAA类别。例如,Imec正在开发一种用于2nm的叉片FET。在叉片FET中,nFET和pFET被集成在同一个结构中。介质壁将nFET和pFET分开。这不同于现有的GAA晶体管,后者的nFET和pFET使用不同的器件。

叉片式FET允许更紧密的n到p间距并减少面积缩放。Imec的2nm叉片具有42nm的接触栅间距(CPP)和16nm的金属间距。相比之下,纳米片的CPP为45nm,金属间距为30nm。

互补FET(CFET)是另一种类型的GAA器件,也是2nm或更高节点工艺的选件。CFET由两个单独的纳米线FET(p型和n型)组成。基本上,p型纳米线堆叠在n型纳米线的顶部。

“ CFET的概念在于'折叠'pFET器件上的nFET,这消除了n-p分离的瓶颈,并因此将单元的有效面积减小了两倍,” Imec的董事Julien Ryckaert表示。

CFET很有前途。副总裁戴维·弗里德(David Fried)表示:“当人们研究GAA技术,特别是堆叠的互补纳米线(CFET)和类似技术时,他们将这些技术创造了一个朝向3纳米、2纳米和1纳米逻辑扩展的拐点,"Lam Research/Coventor公司计算产品副总裁David Fried说。"人们正在回顾堆叠纳米线的发展轨迹,以及下一步如何实现这一转变。这就是人们所想的可能超越3纳米的情况。我不知道有没有人在定义这个空间的节点,但这些技术可能会使3纳米以上的下一个扩展轨迹成为可能。"

不过,CFET和相关晶体管也有一些挑战。TEL公司的高级技术人员杰弗里·史密斯说:“问题在于热过程,在高温过程之前,你需要放很多金属进去。所以,你需要确定CFET的触点和互连之间所需的阻挡金属的最大热极限。"

总而言之,CFET将需要一定的开发时间,因为如今很少有知识可借鉴,而且有很多问题需要解决。IBS首席执行官汉德尔·琼斯(Handel Jones)说:“ CFET前景广阔,但还为时过早。一个大问题是,即使增强了栅极结构,我们也需要增强MOL和BEOL。否则,性能提升将受到限制。”

在2纳米/1纳米制造芯片带来了一系列新的问题,需要在不同的步骤中采用新的技术和设备。这一点在制造过程中应用的薄膜上很明显。

Brewer Science公司技术研究员James Lamb说::“当你开始深入到厚度小于5纳米的自旋涂层层时,你很容易受到表面能微小变化的影响。这可能来自衬底,也可能来自材料。因此,这个确实需要在润湿和被涂基材表面以及被涂材料上做到完美,以确保没有任何缺陷。这些薄膜足够薄,界面动力学控制薄膜的形成,就像在自组装过程中一样,它很容易受到微小变化的影响。”

从这个角度来说,1纳米薄膜可能有5到8个原子的厚度。许多这样的薄膜都在30到40个原子的范围内。

Lamb说:“将其放下,弄湿表面,并使材料粘附到该表面上成为一个挑战。关键的驱动因素是材料的清洁度。如果衬底上有任何变化,那么将会出现异常或局部厚度变化。”

新型EUV光刻机

光刻技术是在芯片上对微小特征进行图案化的技术,有助于实现芯片缩放。在3nm及以后的工艺中,芯片制造商可能将需要一种称为高数值孔径EUV(high-NA EUV)的EUV光刻新版本。

high-NA EUV是当今EUV的扩展,仍在研发中。这种庞大的设备的目标是在2023年达到3nm,相当复杂又相当昂贵。

EUV的重要性有几个原因。多年来,芯片制造商在晶圆厂使用基于光学的193nm光刻机。在多重曝光(multi-patterning)的帮助下,芯片制造商已经将193nm光刻技术扩展到10nm/7nm。但是到了5nm,目前的光刻技术已经失去了发展势头。

这就是EUV的作用。EUV使芯片制造商能够在7nm及更高的温度下设计出最困难的特征。D2S的首席执行官Aki Fujimura说:“在13.5nm波长下使用EUV应该会更容易,也更可行。”

这就是EUV的用武之地。EUV使芯片制造商能够在7nm及以上工艺中构图最困难的功能。在13.5纳米波长下使用EUV应该会更容易、更可行。

EUV一直是难以开发的技术。不过, ASML正在交付其最新的EUV光刻机。该系统使用13.5nm波长和0.33 NA透镜,可实现13nm分辨率,每小时处理170个晶圆。

在7纳米,芯片制造商正在使用基于EUV的单次曝光方法对微小特征进行曝光。单一图案化EUV将扩展到大约30纳米到28纳米的间距。除此之外,芯片制造商还需要EUV双重图案化,这是一个困难的过程。

“即使我们对EUV 应用多重曝光(multi-patterning)技术,覆盖也会非常困难,” Brewer Science的高级技术师Doug Guerrero说。

如果已证明具有成本效益,则在5nm / 3nm及更高波长下,仍然可以选择双重曝光 EUV。但是为了减少风险,芯片制造商更希望使用high-NA EUV,从而使他们能够继续采用更简单的单次曝光。

但是,high-NA EUV很复杂。该系统配备了能够提供8nm分辨率的0.55 NA透镜。high-NA EUV将使用变形镜头,而不是传统的镜头设计。该镜头在扫描模式下支持8倍放大,在另一个方向上支持4倍。结果,场大小减小了一半。因此,在某些情况下,芯片制造商会在两个不同的掩模上处理芯片。然后,将掩模拼合在一起,这是一个复杂的过程。

还有其他问题。没有用于high-NA EUV的抗蚀剂。幸运的是,现有的EUV掩模工具可用于3nm及更高的工艺。

但是,该行业可能需要使用新材料的EUV掩模坯料。反过来,这需要更快的掩模空白离子束沉积(IBD)工具。Veeco产品营销总监Meng Lee说:“我们正在与主要客户积极合作,在我们的IBD系统设计中发布一些先进的功能,这些功能将解决3nm及以后的问题。”

总的来说,high-NA EUV面临数项挑战。Stifel Nicolaus分析师帕特里克·霍(Patrick Ho)表示:“要实现high-NA EUV尚需数年。“ ASML可能会在2021年开始提供beta系统。但是,正如EUV告诉我们的那样,beta系统并不意味着大批量生产就在眼前。”

分子级加工当今的芯片是使用各种原子级加工工具生产的。一种称为原子层沉积(ALD)的技术可一次将材料沉积一层。

原子层蚀刻(ALE)是一项相关技术,可以原子级去除目标材料。ALD和ALE均用于逻辑和存储器。

业界还正在为低于3nm的节点开发ALD和ALE的高级版本。区域选择沉积是一种先进的自对准曝光技术,是一种这样的技术。选择性沉积将新颖的化学方法与ALD或分子层沉积(MLD)工具相结合,涉及在精确位置沉积材料和膜的过程。从理论上讲,选择性沉积可用于在金属上沉积金属,在器件上的电介质上沉积电介质。

潜在地,它可以减少流程中的光刻和蚀刻步骤。但是,在众多挑战中,区域选择性沉积仍在研发中。

即将出现的另一项技术是分子层蚀刻(MLE)。“ ALE自1990年代就诞生了,”阿贡国家实验室的主要材料科学家Angel Yanguas-Gil说。“它是基于等离子体的,但是涉及到各向同性原子层刻蚀的无机材料已经有了发展,这就是我们今天所处的位置。分子层蚀刻是有机/无机杂化材料的延伸。对于半导体行业来说,它提供了一种方法来进行各向同性地减少可用作光刻掩模的材料。”

对于在低个位数纳米节点上开发的芯片,器件选择性增长和去除特定材料都是问题。因此,可以通过某种蚀刻技术消除出现在芯片中的异常现象,但是在这么小的几何尺寸上,晶圆上残留的任何材料都有可能引起其他问题,比如掩膜孔洞堵塞。

业界一直将嵌段共聚物(blockcopolymers)视为生产这些紧密图案化表面的一种方式。当采用嵌段共聚物方法时,会得到非常漂亮的线条,但是它们很粗糙。这种方案的探索依赖于原子层沉积前驱体。

过去,因为无机材料比有机材料更致密、更薄,所以几乎所有的商业努力都集中在无机材料上。但是现在,随着越来越多的有机材料进入到制造工艺中,事情变得越来越复杂。

工艺控制上的挑战

检测和度量也很重要。检测是指使用各种系统查找芯片中的缺陷,而度量则是一种测量结构的艺术。

检测手段分为两类:光学和电子束。光学检测工具速度很快,但是在分辨率上存在一些限制。电子束检测系统分辨率更高,但是速度较慢。

因此,为了结合两者优点,业界一直在开发多光束 / 电子束检测系统,从理论上讲,可以较高的速度实现较高的分辨率,从而找到最难发现的缺陷。

ASML已开发了带 9 个光束的电子束检查工具。但是,芯片制造商希望使用具有更多光束的工具来加快检测过程。

度量技术也面临一些挑战。如今,芯片制造商使用各种系统来测量芯片内的结构,例如微距量测扫描式电子显微镜(CD-SEM)、光学关键尺寸测量(OCD)。CD-SEM 进行的是自上而下的测量,而 OCD 系统则使用偏振光来表征结构。

十年前,许多人认为 CD-SEM 和 OCD 技术会走上绝路,因此,半导体设备行业加快了几种新型度量技术的开发,其中包括称为临界尺寸小角 X 射线散射(CD-SAXS)的 X 射线计量技术。CD-SAXS 使用小光束尺寸的可变角度透射散射,来提供测量结果。X 射线的波长小于 0.1 纳米。

多年来,一些组织已经证明了 CD-SAXS 的良好前景。但是,在某些情况下,X 射线是由研发机构中的大型同步加速器存储环产生的,并没有走到实用化阶段。

显然,对于晶圆厂来说,这些探索都不切实际。晶圆厂需要的 CD-SAXS 工具要使用小巧的 X 射线源。目前有几家公司出售 CD-SAXS 工具,主要用于研发而非生产。英特尔、三星、台积电和其他公司的实验室中都有 CD-SAXS 工具。

面向晶圆厂的 CD-SAXS 工具的问题在于 X 射线源功率有限且速度慢,这会影响吞吐能力。“CD-SAXS 为您提供了芯片内部的惊人轮廓。因为它能穿透基材,所以可以看到不同材料层。” VLSI Research 首席执行官 Dan Hutcheson 说道。“这是一种类似于光学散射法的散射技术,但是它现在的速度很慢。”

除了吞吐能力,成本也是一个问题。“和单纯的光学设备相比,它的价格可能要贵 5 倍或 10 倍。” VLSI Research 总裁 Risto Puhakka 表示。

因此,在一段时间内,至少在逻辑器件上,芯片制造商可能不会将 CD-SAXS 部署在其在线监测工艺中。Puhakka 说:“我们预测,CD-SAXS 在逻辑器件上的商用还需要五年。”

封装技术的演变

IC 工艺尺寸的缩减是推升芯片性能的传统方法,它是在更低的工艺尺寸上实现相同的芯片功能,然后将功能模块封装到单片式的芯片中。

但是,如前所述,先进工艺节点上的芯片设计成本对很多公司都越来越无法承受,而且每一代提供的性能和功耗优势在不断缩小。

“从经济性的角度来看,现在还剩下多少公司可以负担得起先进工艺的价格?这样的公司越来越少了。”联华电子业务管理副总裁 Walter Ng 说。

虽然更先进的工艺仍然是催生新设计的强大手段,但是越来越多的公司却转向了先进封装的性能提升路线。其中,小芯片(Chiplets)是异构集成的另一种形式。

先进封装提升芯片性能正变得可行。比如,在芯片面积至关重要的应用(特别是 AI 应用)中,芯片速度取决于高度冗余的处理元件和加速器阵列,而新工艺能提供的最大好处体现在体系架构的改变和软硬件协同设计上。

对于一个信号而言,从一颗大芯片一端传输到另一端所需的时间,要比使用高速接口垂直传输到另一个裸片上花费的时间更长。

正是基于这种原理,封装公司和代工厂正在改善器件之间的链接性能,并提高封装本身的密度,以进一步提高封装芯片的速度。

台积电通过将小芯片嵌入在前端(FEOL)实现了性能提升。它还计划在 SoIC 中使用先进的混合键合技术。

台积电的方案比使用当下正在使用的硅基内插器连接芯片还要快得多。不过,硅基内插器可以在封装内和封装之间传导光子,从而扩大了它的使用范围。

ASE 副总裁 Rich Rice 说:“现在东西向传输的光纤,已看不到底板,传输并不经过模块的转接,而是直接到达服务器,最后到达交换机。光纤仍然有很大的发展空间,业界的公司正在尝试最新的技术,这将加速光子学的应用。未来的服务器间光纤传输将会具有更多的带宽,而且会出现更多高容量的解决方案,同时它也会变得更便宜。”

和铜线相比,光发送信号所消耗的功率更低。Rice 说:“这将是未来芯片间传输的一种方向,已经有一些公司在研究可传输光信号的内插器。届时,和芯片本身的接口只需要解决将光信号输入到封装侧的问题。”

当然,在芯片中使用光信号比说起来要难多了。光信号将随着芯片的温升而产生漂移,因此需要校准滤波器以解决漂移问题。另外,波导结构的粗糙也会中断光的传输。不过,光信号集成封装的研发已经上路,并非遥不可及。

先进封装技术还具备其它优势。比如,可以在任何理想的工艺节点上开发模拟电路,而且已经设计出来的模拟电路可以重复使用,而不用担心需要缩小模拟芯片的尺寸。

另外,功率半导体器件的封装技术也取得了长足进步。比如,在碳化硅上,供应商实现了将基于碳化硅的MOSFET 和其它组件集成进单个功率模块中。和硅相比,碳化硅的击穿电场更高,热导率也更高。

结论

向 3 纳米的迁移必将发生,只是可能比预期的时间更长而已。这个结论同样适用于 2 纳米。

再往下,目前还说不清楚 1 纳米时会发生什么。可能必须使用 CFET,此外,芯片工艺尺寸的缩减可能就此止步,或者只有很小一部分超高性能、高度专用的芯片或者需要极高密度的小芯片才会用到更先进的工艺。

但是,在短期内,由于没有一种技术可以满足所有应用的需求,所以很多技术都有其发展的空间。

未来智能实验室的主要工作包括:建立AI智能系统智商评测体系,开展世界人工智能智商评测;开展互联网(城市)云脑研究计划,构建互联网(城市)云脑技术和企业图谱,为提升企业,行业与城市的智能水平服务。

??如果您对实验室的研究感兴趣,欢迎加入未来智能实验室线上平台。扫描以下二维码或点击本文左下角“阅读原文”

关注公众号:拾黑(shiheibook)了解更多

[广告]赞助链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

让资讯触达的更精准有趣:https://www.0xu.cn/

关注网络尖刀微信公众号

关注网络尖刀微信公众号随时掌握互联网精彩

- 1 绘就共同富裕新画卷 7904654

- 2 芬兰总理正式向中韩日民众道歉 7808976

- 3 最能生娃省份排名来了 7713437

- 4 这一年 一个个暖心瞬间令人难忘 7617512

- 5 男子入伍火箭军后拒服兵役 官方通报 7523667

- 6 30岁健美冠军去世前几天刚体检完 7429053

- 7 猴子攀绳索过河来 以为表演却是打劫 7333978

- 8 王毅同委内瑞拉外长希尔通电话 7238344

- 9 未婚先孕罚3000?云南奇葩村规被撤 7141020

- 10 海南封关护港 海警全天候执法演练 7045563

人工智能学家

人工智能学家