“大”即正义?详解三星Exynos M3架构

目前移动计算市场中的高性能处理器“玩家”已经所剩不多,除了苹果和华为这样自产自销的厂商外,只有高通、三星还在向第三方厂商提供高性能处理器。三星在2018年1月发布了旗下第三款自研高性能处理器Exynos 9810,采用了全新Exynos M3架构。在三星的描述中,Exynos M3在性能和功耗控制上相比前代产品有大幅进步。那么,Exynos M3究竟在设计方面有什么值得关注的地方,其内部设计又有哪些过人之处呢?本文就来和大家一起探讨这些问题。

三星进入移动处理器市场不算很早。2010年三星在美国得克萨斯州的奥斯汀建立了三星奥斯汀研发中心(Samsung's Austin R&D Center),简称SARC。当时三星从AMD、英特尔和其他芯片厂商招揽了不少人才,开启了自己的高性能移动处理器之路。随后的2012年,首款三星自研高性能处理器架构,也就是Exynos M1开始研发。经过三年多的研发后,以Exynos 8890为名的处理器产品于2016年搭载在三星大受欢迎的手机Galaxy S7上。也正是这一年,三星向外界公布了这个名为“猫鼬Meerkat”的全新处理器架构,人们开始意识到高性能移动计算市场将迎来一位新玩家。

Exynos M1是全新设计的架构,随后三星的数代处理器都基于它打造。随着Exynos M1逐步被淘汰,SARC团队从2015年第一季度开始基于它设计全新的处理器架构,也就是今天的主角Exynos M3。不过在2016年,这个计划曾发生了一次重要变化,因此Exynos M3的性能、功能等重要指标被进一步拔高。

▲三星Exynos M1架构

这个变化是于2015年第三季度出现的Exynos M2,实际上Exynos M2最开始只是Exynos M1的制程优化版本,三星希望用10nm LPE优化Exynos M1,后者采用的是14nm LPP工艺。最终在制程提升和架构小改的情况下,Exynos M2的IPC改进效率竟然达到了20%之多,这使得它的性能远优于Exynos M1,即是芯片频率还降低了12%。三星通过Exynos M2,实现了一些本来计划在Exynos M3中实现的功能,因此Exynos M3的设计就需要变得更具侵略性。

然而三星遇到了半导体业界中最无情的规律:无情的一轮又一轮产品研发周期,尤其是IP和芯片发布必须同步。在这种无情的规律下,很多厂商推出了不那么完美的产品,无论是性能还是功耗,主要原因都是过于严格的商业周期使得产品急于推向市场所致。

要了解Exynos M3,就不得不从Exynos M1开始,实际上这两个架构有颇多相似之处。从Exynos M1到Exynos M3,SARC做出的最大改动在于将微架构宽度从4解码提升至6解码,此外还增增加了整数ALU、第二个负载单元和一个大幅度扩展的浮点/SIMD混合单元,计算容量高达前代产品的三倍。

▲三星Exynos M3架构相关特色总览

由于三星没有公开Exynos M2的体系架构,并且也没有展示与之相关的编译器机器模型,因此在Exynos M2上到底发生了什么变化目前不是很清楚。不过三星透漏的一些消息显示Exynos M2架构的重排序缓冲区已经不再是96队列了,三星对其进行了微调。相应的在Exynos M3上同样功能的模块扩展至228个队列,这种改进类似于英特尔在新一代产品设计中的变化,尽管这些处理器采用了不同的指令集,不过底层的变化还是存在一些共通之处。

▲三星Exynos M3架构和Exynos M1架构存在很深的渊源

另一个证据来自于ARM。ARM最新公布的Cortex-A76的ROB队列入口增加值128,比Exynos M3的ROB看起来小了不少。ARM宣称这是性能和面积、功耗之间平衡的结果,并且给出数据认为ROB增加7%,性能指标只增加1%。

对于这一点,三星解释说,ROB的宽度只是一个选择,它与微架构的其余部分以及各种缓冲区和后端调度程序容量的设计相关联,比如微架构深度和宽度能够相互补充以提高性能。诸如Exynos M3之类的微架构采用的是更宽的方式以便更快地填充ROB,从而获得更多的性能。总的来说,Exynos M3的设计思路和Exynos M1或者Exynos M2还是存在差异的,旨在提高性能的同时降低成本。

接下来深入了解前段部分的更多细节。在Exynos M3上,三星对分支预测单元和指令拾取单元做出了大量的改进。先看分支预测单元。

Exynos M1的分支预测器与其他的微架构存在不同,其主要特点在于每周期采用两个分支并且在后端具有两个分支端口。Exynos M3似乎保持了这个宽度,但是将uBTB从64增加到了128,mainBTB依旧保留了4000链路,不过延迟有所降低,性能表现更出色。

▲Exynos M3架构的前端更大、更宽。

除了设计规格外,Exynos M3的分支预测器的成功率得到了提升,三星宣称Exynos M3的分支预测错漏值平均减少了15%。为了证明这个说法,三星发布了一个被称为MPKI的值,也就是Misses per kilo instructions每千指令错漏数据值,这个数据的出现有点突然,实际上就连ARM也没有采用这样的统计方法,三星解释MPKI的数据来源是通过监控来自各种应用程序和用例的不断扩展的4000~6000种代码,跟踪分支预测器的性能最终得出。具体数值方面,Exynos M3为3.29,Exynos M2位3.92,也就是说Exynos M3的每千指令错漏数据值显著降低了。

另外,分支预测单元和拾取单元分别提供一个解耦的地址队列和一个解耦的指令队列,这样做的优势在于这些单元可以进行时钟门控以在必要的时候节约能源。

拾取单元的带宽也已经加倍,现在每周期最多可以读取48个字节,相当于每周期12个32bit指令—这导致拾取单元和解码单元的容量比率为2∶1,比之前M1中1.5∶1的比率有所增加。三星解释说,由于需要应对越来越严重的分支气泡问题,因此需要大幅度增加微架构的成本。三星也承认,平均而言所采用分支的距离小于12条指令,但是较大的宽度对临时的指令突发具有很好的帮助。

随着这种变化的瞬时功率利用率很高,但是当指令队列被填充满甚至比解码单元的处理速度更快时,由于时钟门控的存在,它对功耗表现具有正面的影响。在这里,整体的能效和分支预测器更加紧密相关,因为获取指令时能耗实际上不重要,只有在更大的“批处理”存在时,在错误分支路径出现时,抛弃指令可能会导致功耗增加。

L1指令缓存部分为64KB,目前还不确定这个是否比Exynos M2增加,但是肯定是Exynos M1微架构的2倍。

指令后备缓冲区(ITLB)已经从256个条目增加到512条目,需要注意的是,三星正在采用三层结构,而不是我们在ARM处理器中看到的结构。Cortex-A75和Cortex-A76分别具有第一季32条和48条uITLB,其中mainTLB一共有1280条目,包括一个1024条目的主表和一个256条目的副表。

三星也提到了一级数据和指令TLB,但是没有透露它的大小。三星的最后一级统一TLB拥有4096个条目,后文还会提及到它。

在架构的中端(三星称之为mid-machine,中机),我们看到了Exynos M3的6宽度解码单元。三星在此处没有披露太多的细节,但是宣称改进了指令/uOP的融合功能。重命名和调度吞吐量已经重设计以匹配解码宽度。Exynos M3支持Exynos M1的多调度形式,也就是解码器发出一个uOP,可以同时调度至多个调度程序,但是它依旧只计算为一个调度和一个条目。

▲Exynos M3架构中机部分的特性

在整数核心中,Exynos M3设计了两个额外的调度器,因此Exynos M3现在能够再前几代7个的基础上将uOps继续提升到9,其中一个新的端口是具有乘法功能的附加ALU单元,这使得MUL的吞吐量加倍,并将简单整数算术吞吐量提高了25%。辅助的附加端口是第二个AGU,者能够使核心的负载带宽加倍。

▲Exynos M3架构的核心流水线示意图

在浮点核心方面,和之前的微架构相比,三星设计了一个与众不同的“巨兽”。三星在Exynos M3上增加了第三条管道,增加了在FPU中分派和发布的uOPs。单纯就浮点能力而言,Exynos M3在Exynos M1的 FMAC+FADD的基础上,又增加了3个128bit的FMAC/FADD单元,是的乘法和算数吞吐量增加了三倍之多。就FLOPS而言,这表示从3FLOPS(1xFMAC(2)+1FADD)增加到6FLOPS(3*FMAC(2)),最大吞吐量加倍。

▲Exynos M3架构大幅度加强了浮点部分

当然因为浮点吞吐量句句增加,所以必须扩展调度程序和物理寄存器以适应这种增加的幅度,Exynos M3将调度窗口从之前的32增加到了63,FP PRF大小也从之前的96扩展到了192。

三星也一直在努力减少延迟,这也适用于浮点流水线。在这里,乘法单元的周期已经从之前的4个缩减至3个,FMAC从之前的5个下降到了4个,简单浮点的周期从3缩减至2,浮点除法单元Radix-64经过了升级,降低了计算延迟。

在这里需要指出的是,ARM虽然在Cortex-A76中大肆宣传全新的浮点管道,并为他们新的VX数据路径感到自豪。但实际上从较高的级别来看,三星似乎在Exynos M3上就实现了相似功能,因为Exynos M3具有和Cortex-A76相同的浮点延迟,同时具有更高的执行吞吐量以及更低延迟的ASIMD。

Exynos M3的加载/存储单元由于增加了第二个128bit的端口,因此读取带宽翻倍,负载延迟则维持之前的4个周期不变。存储方面,延迟为每周期存储一次延迟仅为1个周期。同样,Exynos M3依旧具有双带宽优势,因为它的两个LD单元以128bit/周期的方式进行工作,相比之下Cortex-A75只有64bit/周期,只有最新的Cortex-A76升级到了128bit/周期。

▲Exynos M3设计了全新的加载和存储单元

总体而言,由于LD/ST调度程序的容量已经增加,因此缓冲区也相应增加了一倍。为了更好服务于新的更大规模的微架构,L1数据高速缓存上的未解决的未命中数据值从8增加到12,这意味着在高速缓存未命中旗舰,该单元可以提供多达12个并发数据请求,核心/系统能够从更高层级的缓存或者内存中获取数据。

考虑到Exynos M3的微架构宽度,这种可能性似乎很低。相比之下,ARM没有公开披露Cortex-A75相应的规格,但是他们将MLP/内存级并行作为Cortex-A76的一个重点,后者的L1D可以提供多达20个未解决的未命中数据存储,这比Exynos M3更多,即使其宽度要更窄一些。

由于三星独特的设计,因此它的预取器设计需要具有最高质量,以避免任何内存瓶颈的存在,并实现最佳缓存命中操作。实际上三星“混合”预期器已经有所增强,在这里“混合”的意思意味着能够处理不同类型内存模式的单个预取器。

在数据方面,三星提到了新的TLB层级结构的相关内容。Exynos M3使用了和Exynos M1相同的32-entry的micro-DTLB设计,以及一个全新的、拥有512-entry的中等DTLB。指令TLB和数据TBL目前都有增强过的、容量更大的统一L2 TLB服务,这个L2 TLB拥有4096-entry,相比前一代的1024翻了两番。

扩大位处理器架构是需要付出代价的,和Exynos M1架构相比,Exynos M3在管道深度上增加了2个周期,添加了辅助调度阶段,以及用于寄存器读取的第二阶段。通常CPU流水线深度计算方法是从预测/分支一直到寄存器回写,在这种计算方法下,Exynos M3的拥有17级流水线,已经非常深了。Exynos M1只有15级,而Cortex-A76和Cortex-A75都只有13级。

对Exynos M3架构来说,分支预测错误的惩罚周期是16,相比之下流水线级数更少的Exynos M1只有14个周期。三星没有透露Exynos M3的微架构是否在各个阶段之间有什么快速路径来接解决关键情况下的延迟问题,Exynos M3和Exynos M1的部分缺点是相比ARM公版,它的拾取和解码单元比ARM多了2级,寄存器重命名单元多1级以及需要第二个调度阶段(再多1级)。三星承认这虽然是一个负面因素,但是为了让更宽、更大的微架构能按照计划完成,这样做也是必要的。

总的来说,奇怪的是三星虽然采用了更深的流水管线,但是实际上并没有在具体的产品中产生出更为明显的频率效应。一般来说流水线级数越多、管线越深,物理频率上限会越高。Exynos M3目前在频率和功耗上的表现,让人们怀疑三星是不是遇到了什么问题。

在CPU核心之外,Exynos M3的三级缓存结构体系也值得一看。和Cortex-A76一样,Exynos M3引入了新的私有L2缓存作为核心和最后一级共享缓存之间的中间级别,新的L2缓存每个核心的容量为512KB。访问延迟方面,Exynos M3的访问延迟只有12个周期,这比Exynos M1的22个周期大幅度降低,但是依旧不如ARM公版,ARM公布的Cortex-A75的L2访问延迟只有8个周期。值得注意的是,在实际的物理实现中,这个数字可能会上升,比如骁龙845在2.8GHz时延迟大约为4.4ns,而2.7GHz的Exynos 9810的延迟大约为4.6ns。带宽方面,Exynos M3的L2缓存带宽也增加了一倍,目前实现了32Bit/周期,而之前的Exynos M1则为16Bit/周期。相比之下,Cortex-A75的L2读取为16Bit/周期,写入为32Bit/周期。

▲Exynos M3架构的新三级缓存结构体系

在缓存布局方面,Exynos M3的布局和ARM官方要求存在很大差异。ARM实际上并未允许第三方核心使用DynamiQ/L3缓存系统,所以Exynos M3的相关设计和ARM是没有任何关系的。

Exynos M3在L3缓存设计上采用了NUCA也就是非同一缓存架构的方案。Exynos M3的L3缓存总计为4MB,分为4个1MB的片区,每个片区分别位于CPU核心的对面。由于布局不均匀,核心和不同缓存片区之间的访问延迟是有差异的。核心和相邻最近的缓存片区访问延迟仅为32个周期,最远的片区则有44个周期的延迟,三星在典型模式中使用37个周期作为其平均延迟。

和ARM的相关设计相比的话,Exynos M3似乎要更弱一些。Cortex-A75的L3缓存周期仅为25个,实际产品比如骁龙845为11.4ns左右,而Exynos 9810则从11ns左右开始,最长则达到20ns左右。实际上三星的L3缓存实现并受到CPU高频率的影响较小,因为缓存的布局影响了延迟。

对于这种情况,三星解释说这种缓存切片的设计方案旨在为高端移动设备之外的不同设计实现更好的可配置性,考虑到三星在汽车行业的野心,这种说法也是有可能的。对于缓存层次结构而言,三星承认最终产品可能没有达到他们想要的水平,因为L3缓存设计必须考虑各种因素,权衡利弊非常重要。希望三星在下一代产品设计上做得更好。

三星还特别公布了Exynos M1和Exynos M3两代核心的相关核心布局图,由于原本数据为英文,本文对一些图片中涉及到的特殊的名词翻译如下:

pL2:专属L2缓存,图片中有512KB缓存,分为两个区块。

FPB:浮点数据路径,是指FP和ASIMD执行单元。

FRS:浮点调度程序和FP/向量物理寄存器。

MC:三星称其为“中核”,主要是指解码器和重命名单元。

DFX:至调试/测试逻辑,比如DFD是调试设计、DFT是指测试设计、DFM是其它杂项逻辑。

LS:加载、存储单元,包含64KB L1高速缓存。

IXU:整数执行单元,包含执行单元、调度程序和整数物理寄存器。

TBW:透明缓冲区写入,包含TLB。

FE:前端,包括分支预测器、拾取单元和64KB L1指令缓存。

▲Exynos 9810的整个核心平面图

▲Exynos 9810的单个核心平面图

总体而言,和Exynos M1相比,Exynos M3中功能单元几乎所有方面的尺寸都大大增加,最终产品尺寸为2.52平方毫米用于内核,还有0.98平方毫米的512KB L2缓存。

▲Exynos M1架构的核心布局图

▲Exynos M3架构的核心布局图

在图形之外,三星还特别提及了对新架构的性能和工作负载的评估。根据三星的数据,Exynos M3核心的最终IPC增长数字大约为59%,正如三星在图片中展示的那样,所有的工作负载增长都不是线性的,在高ILP下工作负载增长仅为25%,而MLP工作负载可能没有增加。在一部分混合负载中,IPC增加能够高达80%。

▲Exynos M3架构的IPC提升情况

▲Exynos M3架构的每瓦特性能情况

▲进一步分析Exynos的CPU集群

▲Exynos M3架构和Cortex-A75以及Exynos M2架构的性能对比

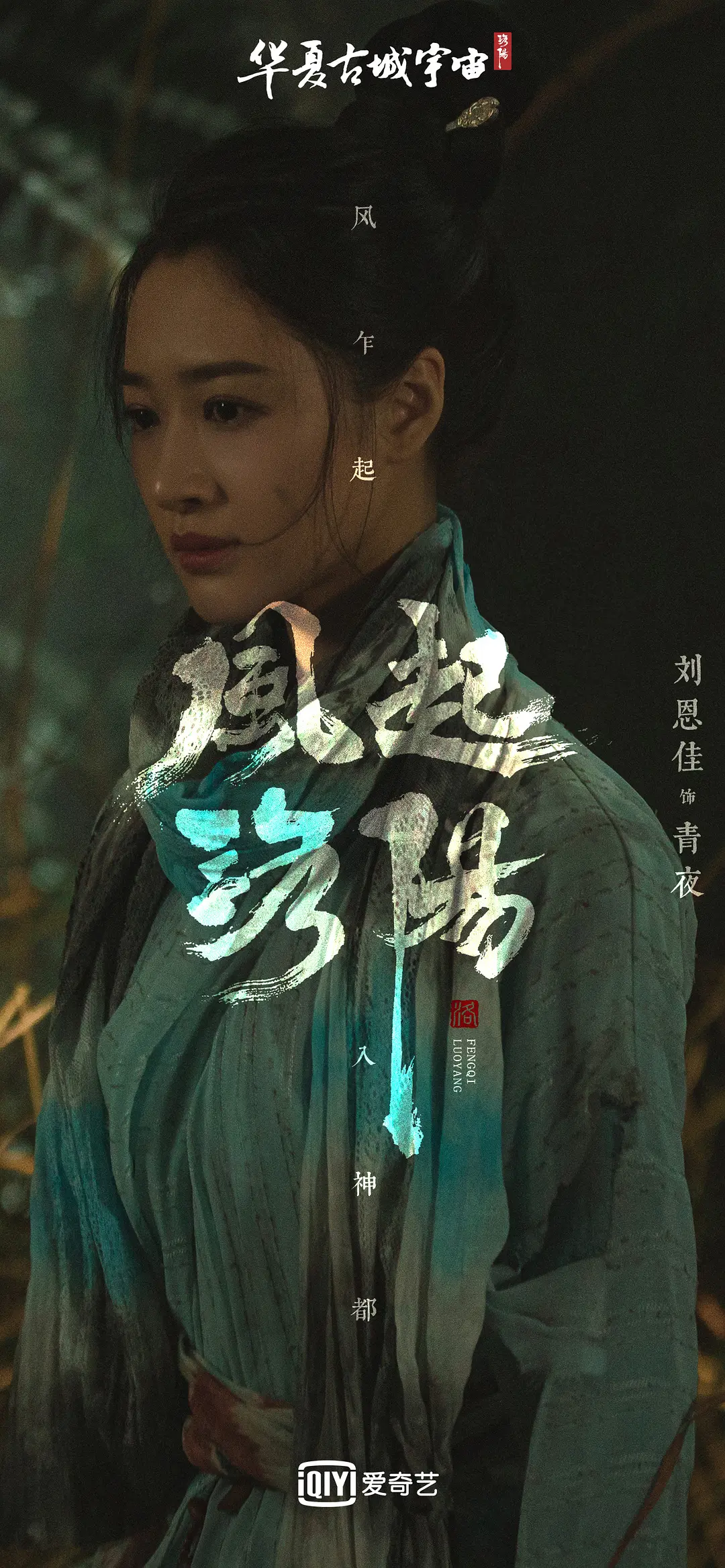

Exynos M3对三星的设计团队来说是一次大挑战,整个架构几乎重制,并且必须面对时间压力。xynos M3原本从2014年第二季度开始,但是随着Exynos M1的完成和Exynos M2的出现,计划发生改变,Exynos M3原本的部分设计被分配给Exynos M2,这导致Exynos M3设计异常激进。

Exynos M3在2016年第一季开始修订,2017年第一季度需要交付RTL给SoC团队,用于Exynos 9810的第一个EVT0流片。请注意,最终的商用版本是RVT1,其流片完成在2017年中期,商业版本的Exynos 9810在2018年3月最终上市。从开始规划到设计完成,基本上用了一年左右时间。

从架构角度来看,Exynos M3设计还是相当出色的,它的体系结构非常坚实,给人的感觉更像是一颗高性能桌面级处理器。三星似乎在调整微架构性能方面采用了最直接的方法,那就是设计一颗更大的芯片来满足各种需求。大就是好,虽然在Exynos M3上还有一些不成熟的地方,但是这个规模巨大的架构基础已经完成。

在Exynos M3之后,三星的SARC团队现在每年都会推出新的产品,接下来三星还将推出M4架构。从三星架构延发的过往来看,Exynos M2和Exynos M3的IPC增长分别为20%和59%,考虑到ARM接下来的新架构承诺增长大约10%~15%的性能,因此Exynos M3的继任者M4有可能在性能和功耗表现上超过ARM公版架构。最后,希望三星能够解决Exynos M3架构和Exynos 9810的弱点,推出新的架构并带来移动计算的新一轮性能增长。

关注公众号:拾黑(shiheibook)了解更多

[广告]赞助链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

让资讯触达的更精准有趣:https://www.0xu.cn/

关注网络尖刀微信公众号

关注网络尖刀微信公众号随时掌握互联网精彩

- 1 坚持打铁必须自身硬 7985305

- 2 山西临汾地震 7998584

- 3 鲁GT8586你真帅 7891933

- 4 瞄准全方位扩大内需持续发力 7798222

- 5 黄圣依发文没有一句提杨子 7629490

- 6 陈奕迅演唱会曼谷站取消 将全额退款 7567008

- 7 雷军:特斯拉Model Y也不错 7476521

- 8 李行亮:录完节目我们觉得很羞耻 7357059

- 9 男子10岁时烫伤疤痕60多年后癌变 7251201

- 10 苏有朋春晚彩排 爷青回 7102721

微型计算机

微型计算机